Surrounding Gate voor 5nm-SRAM

11 juni 2018

op

op

Het Belgische onderzoeksinstituut Imec heeft in samenwerking met de firma Unisantis uit Singapore SGT’s (Surrounding Gate Transistors) ontwikkeld, waarmee SRAM-cellen opgebouwd uit zes transistoren mogelijk zijn in 5nm-technologie.

Alles draait om miniaturisering in de halfgeleidertechniek. De Wet van Moore is nog steeds van kracht, maar leidt er wel toe, dat de afmetingen van de structuren op halfgeleiderchips steeds dichter naderen tot de grootte van atomen. Een verticale Surrounding Gate Techology van Unisantis maakt het nu mogelijk om een SRAM-cel die bestaat uit zes transistoren op te bouwen op de ongelofelijk kleine oppervlakte van 0,0184 tot 0,0205 μm². Zo’n op SGT’s gebaseerde cel neemt 20 tot 30 % minder chipoppervlak in dan een horizontale SGT. Bovendien biedt deze opbouw voordelen voor de voedingsspanning en de stabiliteit.

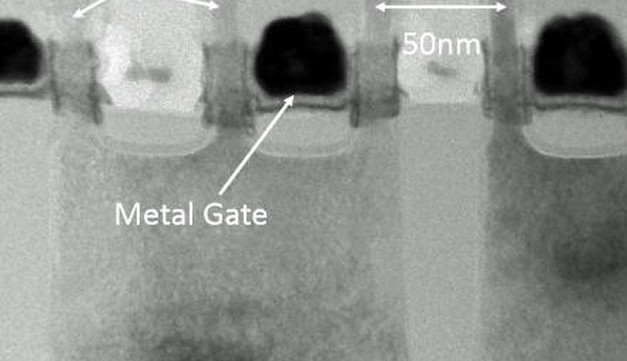

SGT’s (Surrounding Gate Transistors) van Unisantis

Met de verticale Surrounding Gate wordt een bijna perfecte aansturing van het kanaal van de FET bereikt. Een daarmee opgebouwde SRAM-cel past op een oppervlakte van maar 0,0205 μm² bij een minimale Pillar Pitch van 50 nm, wat een 24 % betere benutting van de oppervlakte betekent in vergelijking met de kleinste conventionele SRAM-cellen. De fabricagekosten zouden vergelijkbaar zijn met die van conventionele finFET-SRAM’s, als het aantal processtappen met EUV-lithografie beperkt wordt gehouden.

Alles draait om miniaturisering in de halfgeleidertechniek. De Wet van Moore is nog steeds van kracht, maar leidt er wel toe, dat de afmetingen van de structuren op halfgeleiderchips steeds dichter naderen tot de grootte van atomen. Een verticale Surrounding Gate Techology van Unisantis maakt het nu mogelijk om een SRAM-cel die bestaat uit zes transistoren op te bouwen op de ongelofelijk kleine oppervlakte van 0,0184 tot 0,0205 μm². Zo’n op SGT’s gebaseerde cel neemt 20 tot 30 % minder chipoppervlak in dan een horizontale SGT. Bovendien biedt deze opbouw voordelen voor de voedingsspanning en de stabiliteit.

Met de verticale Surrounding Gate wordt een bijna perfecte aansturing van het kanaal van de FET bereikt. Een daarmee opgebouwde SRAM-cel past op een oppervlakte van maar 0,0205 μm² bij een minimale Pillar Pitch van 50 nm, wat een 24 % betere benutting van de oppervlakte betekent in vergelijking met de kleinste conventionele SRAM-cellen. De fabricagekosten zouden vergelijkbaar zijn met die van conventionele finFET-SRAM’s, als het aantal processtappen met EUV-lithografie beperkt wordt gehouden.

Read full article

Hide full article

Discussie (0 opmerking(en))