Gratis artikel: Nieuwe CPLD-print met MAX10 – meer logica met de MAX10-familie

op

Deze opgevoerde versie van onze CPLD-print heeft met de MAX10M08 niet alleen een CPLD aan boord met meer logische elementen dan zijn voorganger, maar het IC bevat ook typische FPGA-functies zoals PLL’s, ADC’s en softcore-microcontrollers.

In Elektor 5-6/2018 presenteerde de auteur een print met een CPLD uit de MAX-II-familie van Altera (tegenwoordig Intel). De op deze print gemonteerde EPM570 is een CPLD met 570 logische elementen (LE) in een TQFP100-behuizing, maar de print ondersteunt ook de kleinere EPM240 die dezelfde pen-layout heeft. De relatief kleine IC-behuizing maakte het mogelijk om de print als een soort DIL-IC op prototype-boards te plaatsen.

Weliswaar kan met de 570 LE een heleboel logica worden gebouwd, maar soms is het niet genoeg, en daarom gingen we op zoek naar een andere CPLD-familie. Omdat de MAX-V-reeks weinig voordelen biedt ten opzichte van de MAX-II-familie, is het handiger om direct over te stappen op Intel’s actuele CPLD-familie MAX10. Deze familie bestaat uit zeven CPLD-productgroepen, ieder met zijn eigen varianten. Er is keuze uit 2K tot 50K logische elementen, enkelvoudige of dubbele voeding met geïntegreerde 3,3V-LDO (bij het hier gebruikte model is alleen Single Power Supply mogelijk), flash-geheugenblokken van verschillende grootte, analoog/digitaal-converters (ADC’s), een temperatuursensor, dual-configuration flash (twee dynamisch te gebruiken images op één chip) en nog veel meer.

Van CPLD tot FPGA

De MAX10-familie beschikt naast afzonderlijke CPLD-functies ook over volledige FPGA-functies zoals (maximaal vier) interne PLL’s om hogere klokfrequenties te genereren, softcore-microcontrollers (NIOS), DSP-blokken (Digital Signal Processing) en soft-DDR3-geheugencontrollers.Al deze varianten zijn in verschillende behuizingen (van kleine ‘wafer’-behuizingen tot grote exemplaren met honderden I/O-pennen) beschikbaar. Dit is ook meteen ons eerste keuzecriterium: De enige voor hobbyisten met de hand nog soldeerbare behuizing is namelijk de EQFP met 144 aansluitingen. Door deze behuizing met afmetingen van 22 x 22 mm2 wordt de print weliswaar iets groter dan zijn voorganger, maar beschikt in ruil daarvoor (in alle varianten) over 101 bruikbare I/O’s. Meer (gedetailleerde) informatie is te vinden in het handboek van de MAX10-familie.

Periferie

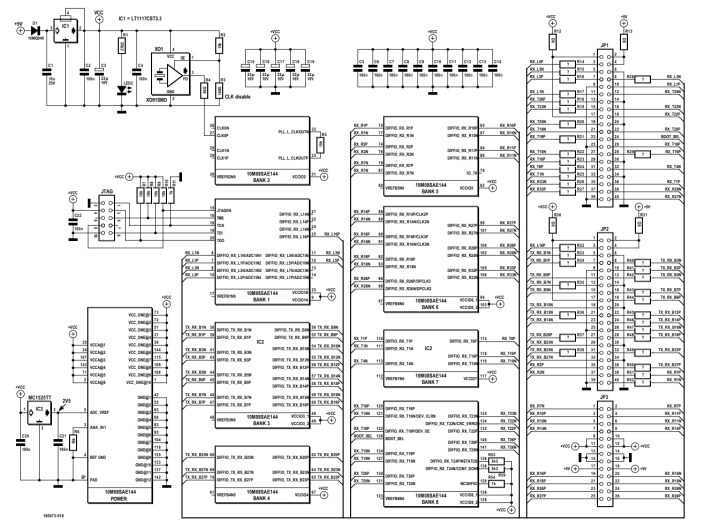

Net als zijn kleinere voorganger bevat deze print, zoals in het schema van figuur 1 is te zien, naast de nieuwe CPLD ook een spanningsregelaar inclusief afvakcondensatoren, een klokoscillator en een JTAG-connector voor het programmeren. Daarnaast is er ook een spanningsreferentie aanwezig voor de in de CPLD geïntegreerde A/D-converter (Bank 1A).

Net als bij het eerdere model zijn ook hier niet alle I/O’s met de connectoren verbonden en dat heeft een goede reden: het board kan weliswaar als een groot DIL-IC op een breadboard of gaatjesprint worden geplaatst, maar de clou is eigenlijk dat de twee(!) pen/busheaders dezelfde layout hebben als de 2 x 20-polige I/O-connector van een Raspberry Pi (vanaf versie 2) en daardoor direct op deze minicomputer kunnen worden geplaatst. Hiermee worden de rekenkracht en de PC-interfaces van de Raspberry Pi gecombineerd met de hardwaremogelijkheden van een moderne CPLD. In figuur 2 ziet u de penlayout van de drie connectoren (met de CPLD-pennen) en ter vergelijking de GPIO-connector van de Raspberry Pi. Naast elkaar liggende aansluitingen met dezelfde kleur vormen een differentieel in- of uitgangspaar, maar kunnen natuurlijk ook (net als de niet-gekleurde aansluitingen) afzonderlijk worden gebruikt.

Ook de bevestigingsgaten passen precies.

Combinaties

Er zijn dus veel combinatiemogelijkheden: de print kan, zoals in figuur 3 is te zien, in zijn geheel op de RPi worden geplaatst, waarbij ook de bevestigingsgaten overeenkomen. Connector JP1 is als busheader aan de onderkant gemonteerd en met de GPIO’s van de Raspberry Pi verbonden. De twee andere connectoren zijn als pinheaders aan de bovenkant gemonteerd en vrij toegankelijk.Figuur 4 laat zien hoe de RPi via JP2 de CPLD aanstuurt, en deze op zijn beurt via JP1 met de elektronica (bijvoorbeeld vermogensdrivers) op een gaatjesprint is verbonden. De voeding van de twee printen kan worden gecombineerd of gescheiden worden gehouden. Dit wordt ingesteld met de 0-Ω-weerstanden R12, R13, R30 en R31.

➔ Wilt u meer ElektorLabs artikelen lezen? Word dan nu lid van Elektor!

Discussie (0 opmerking(en))