Record: laagste vermogen in embedded SRAM

13 juni 2017

op

op

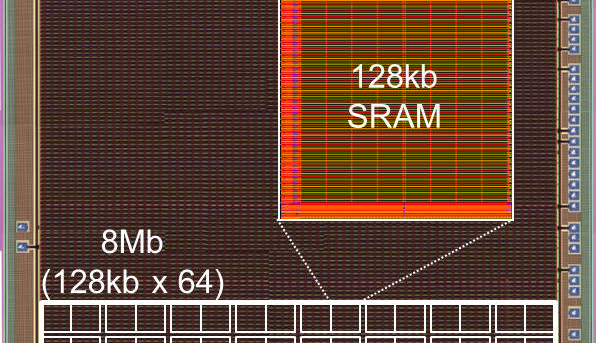

Renesas claimt met 13.7 nW/Mbit een nieuw record als laagste stand-by vermogen voor embedded SRAM . De snelheid van 1,8 ns voor actief uitlezen is daarbij gehandhaafd. Het bedrijf geeft aan dat het zijn eigen Silicon On Thin Buried-oxide-proces (SOTB) heeft gebruikt voor het prototype en met substrate biasing een compromis tussen lekken en snelheid heeft ingesteld. Deze technologie zou de problemen die zich voordoen met conventionele CMOS , zoals meer lekkage bij transistors met een lage drempelspanning en grotere variabiliteit van de gate-drempelspanning, kunnen tegengaan.

Een belangrijke bron van drempelspanningsvariatie in conventionele kleine transistors is dat er zo weinig atomen van het doteringsmateriaal in het kanaal zitten, dat een paar meer of minder de drempelspanning al doen veranderen. Met STOB en andere Fully-Depleted Silicon-on-Insulator (FDSoI)-processen, zouden er geen doteringsatomen in het kanaal van de transistor voorkomen.

Bij het veranderen van normale naar hogesnelheidsmodus (van zero substrate bias naar forward bias) verandert de toegangstijd bij het lezen met de nieuwe chip van 4,58 naar 1,84 ns.

Omgekeerde bias in stand-by-modus vermindert de lekkage met een factor 1000 in vergelijking met normale modus tot de nieuwe recordwaarde van 13,7 nW/Mbit.

Het onderzoekswerk dat heeft geleid tot dit prototype is gepresenteerd bij de VLSI-Symposia in Kyoto op 8 juni. Renesas verwacht deze technologie te kunnen gebruiken als een alternatief voor niet-vluchtig geheugen voor energy-harvesting en batterijgevoede toepassingen in IoT, domotica en gezondheidszorg.

Een belangrijke bron van drempelspanningsvariatie in conventionele kleine transistors is dat er zo weinig atomen van het doteringsmateriaal in het kanaal zitten, dat een paar meer of minder de drempelspanning al doen veranderen. Met STOB en andere Fully-Depleted Silicon-on-Insulator (FDSoI)-processen, zouden er geen doteringsatomen in het kanaal van de transistor voorkomen.

Bij het veranderen van normale naar hogesnelheidsmodus (van zero substrate bias naar forward bias) verandert de toegangstijd bij het lezen met de nieuwe chip van 4,58 naar 1,84 ns.

Omgekeerde bias in stand-by-modus vermindert de lekkage met een factor 1000 in vergelijking met normale modus tot de nieuwe recordwaarde van 13,7 nW/Mbit.

Het onderzoekswerk dat heeft geleid tot dit prototype is gepresenteerd bij de VLSI-Symposia in Kyoto op 8 juni. Renesas verwacht deze technologie te kunnen gebruiken als een alternatief voor niet-vluchtig geheugen voor energy-harvesting en batterijgevoede toepassingen in IoT, domotica en gezondheidszorg.

Read full article

Hide full article

Discussie (0 opmerking(en))