Eerste industriële RISC-V SoC FPGA architectuur brengt real-time naar Linux, geeft ontwerpers de vrijheid te innoveren in laagvermogen, veilige en betrouwbare ontwerpen

3 december 2018

op

op

Belangrijkste eigenschappen:

- Demonstraties tijdens RISC-V Summit, 4-5 december, toont afmetingen, verbruik en prestatievoordelen

- Integreert PolarFire SoC’s hard CPU subsysteem met programmeerbare logica

- Nieuwe klasse van SoC FPGA’s levert real-time voorspelbaar gedrag op een veelzijdig Linux platform

- Mi-V embedded experts programma ondersteunt klanten wereldwijd bij PolarFire SoC ontwerpen

Via de dochteronderneming Microsemi Corporation kondigt Microchip een uitbreiding aan van het

Mi-V ecosysteem met het onthullen van de architectuur voor een nieuwe klasse van SoC FPGA’s tijdens de RISC-V Summit, gehouden van 4 tot 5 december 2018. De nieuwe serie combineert de industriële mid-range PolarFire™ FPGA serie met een compleet microprocessor subsysteem gebaseerd op de open, royalty-vrije RISC-V instructiesetarchitectuur (ISA) die tevens het laagste vermogen opneemt.

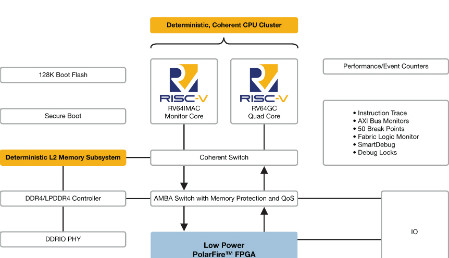

Aangekondigd op de RISC-V Summit in Santa Clara, California, brengt Microchip’s nieuwe PolarFire SoC architectuur real-time voorspellende asymmetrische multiprocessing (AMP) verwerking naar Linux systemen in een cluster van meerdere kernen omvattende coherente centrale verwerkingseenheden (CPU’s). De PolarFire SoC architectuur, ontwikkeld in samenwerking met SiFive, voorziet in een flexibel 2 MB L2 geheugensubsysteem dat kan worden geconfigureerd als een cache, kladblok of een direct toegankelijk geheugen. Hiermee kunnen ontwerpers voorspellende real-time embedded toepassingen implementeren, simultaan met een veelzijdig besturingssysteem voor allerhande toepassingen die weinig ruimte vergen en niet mogen opwarmen in samenwerkende en in een netwerk opgenomen IoT systemen.

Op een nieuw terrein van informatieverwerking, aangestuurd door het in één punt samenkomen van 5G, zelflerende machines en het internet der dingen (IoT), hebben ontwerpers van ingebedde systemen behoefte aan de veelzijdigheid van op Linux gebaseerde besturingssystemen. Deze moeten voldoen aan voorspelbare systeemeisen in thermisch beperkte ontwerpomgevingen met een almaar lagere vermogensopname, maar tevens voldoen aan kritische veiligheids- en betrouwbaarheidseisen. Traditionele systeem-op-chip (SoC) veldprogrammeerbare poortschakelingen (FPGA’s) bieden een mix

Read full article

Hide full article

Discussie (0 opmerking(en))